IEEE EDS/PHO Columbus DL Speaker: Low Power IC Design for a Sustainable World (Grimblatt)

To view complete details for this event, click here to view the announcement

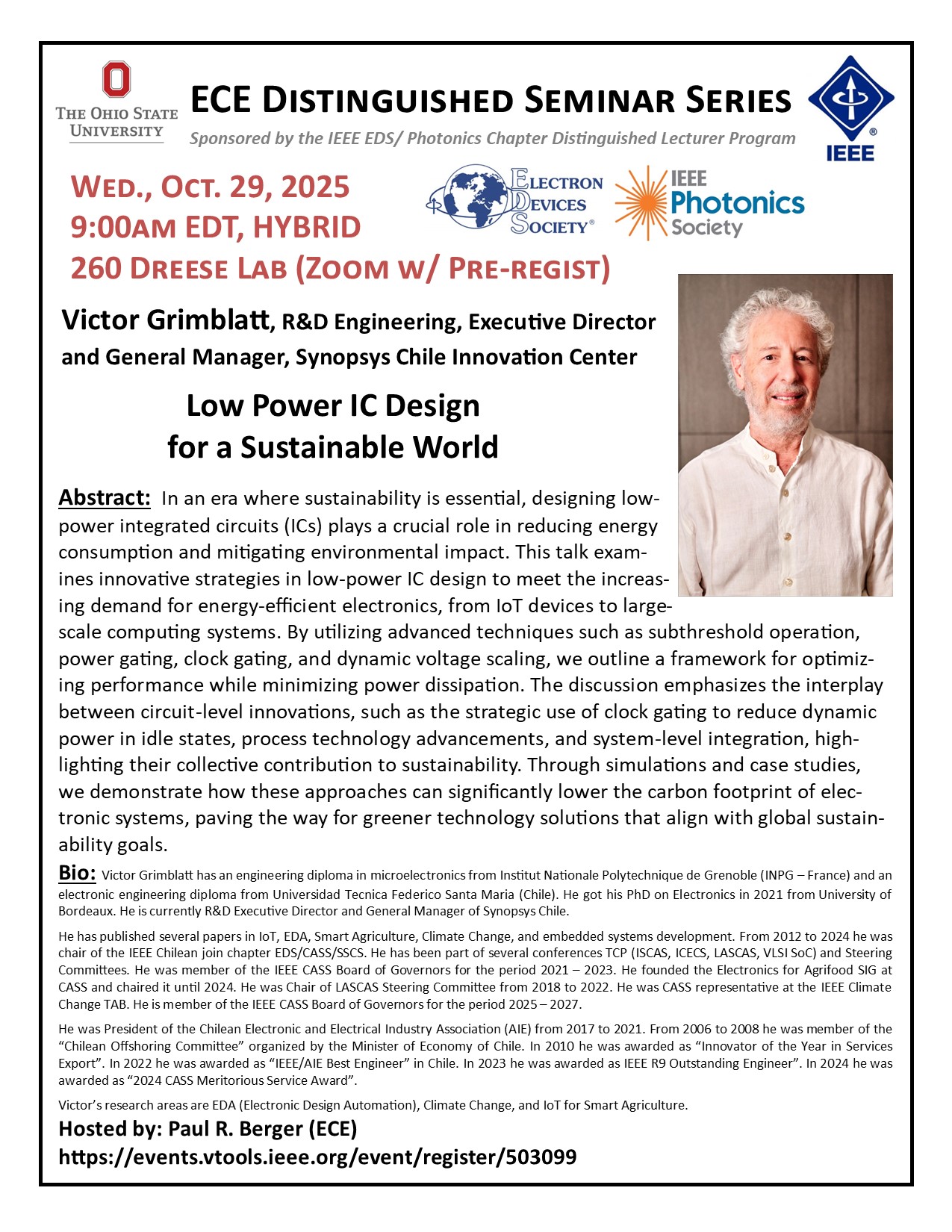

IEEE EDS/PHO Columbus DL Speaker: Low Power IC Design for a Sustainable World (Victor Grimblatt, Ph.D., Synopsys Chile Innovation Center)

Abstract: In an era where sustainability is essential, designing low-power integrated circuits (ICs) plays a crucial role in reducing energy consumption and mitigating environmental impact. This talk examines innovative strategies in low-power IC design to meet the increasing demand for energy-efficient electronics, from IoT devices to large-scale computing systems. By utilizing advanced techniques such as subthreshold operation, power gating, clock gating, and dynamic voltage scaling, we outline a framework for optimizing performance while minimizing power dissipation. The discussion emphasizes the interplay between circuit-level innovations, such as the strategic use of clock gating to reduce dynamic power in idle states, process technology advancements, and system-level integration, highlighting their collective contribution to sustainability. Through simulations and case studies, we demonstrate how these approaches can significantly lower the carbon footprint of electronic systems, paving the way for greener technology solutions that align with global sustainability goals.

Date and Time

Add Event to Calendar

Add Event to Calendar

Location

- This event has virtual attendance info. Please visit the event page to attend virtually.

- Department of Electrical and Computer Engineering

- 2015 Neil Avenue

- Columbus, Ohio

- United States 43210

- Building: Dreese Lab

- Room Number: 260

Hosts

Registration

- Starts 25 September 2025 12:00 AM EDT

- Ends 28 October 2025 10:00 PM EDT

- No Admission Charge

Speakers

Victor

Victor Grimblatt, Ph.D.